## Fifth Semester B.E. Degree Examination, Dec. 2013 / Jan 2014. Fundamentals of CMOS VLSI

Time: 3 hrs. Max. Marks:100

Note: Answer any FIVE full questions, selecting atleast TWO questions from each part.

## PART - A

- 1 a. Explain the fabrication steps of CMOS P well process with neat diagram and write the mask sequence. (12 Marks)

- b. List the threshold voltage equations and emphasize each term. (08 Marks)

- 2 a. Write the CMOS inverter circuit and briefly explain. Write the CMOS VTC showing regions A, B, C, D, E. Derive the expressions for output voltage in region 'B'. (10 Marks)

- b. Write the circuit and layout for  $Y = \overline{AB + CD + E}$  in CMOS style. (10 Marks)

- 3 a. Write the circuit and stick diagram for CMOS tristate inverter. (04 Marks)

- b. Write the circuit of Bi CMOS NAND and NOR gate and briefly explain. (08 Marks)

- c. Explain the circuit of dynamic CMOS logic by taking an example of the function  $Y = \overline{A(B+C) + DE}$ . (08 Marks)

- a. Define Sheet Resistance (Rs) and standard unit of capacitance ( $\square$ Cg). Calculate the on resistance of 4:1 nmos inverter with Rs =  $10k\Omega / \Omega$ ,  $Z_{pu} = \frac{8\lambda}{2\lambda}$ ,  $Z_{pd} = \frac{2\lambda}{2\lambda}$ . Also estimate the total power dissipated if  $V_{DD} = 5V$ .

- b. Calculate the capacitance in  $\Box$  Cg for the given metal layer shown in fig.Q4(b), if feature size =  $5\mu$ m and relative value of metal to substrate = 0.075. (05 Marks)

c. Explain briefly the circuit of inverting and non – inverting super buffer.

(07 Marks)

## <u>PART - B</u>

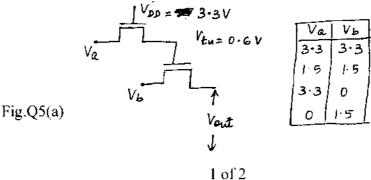

5 a. Calculate the O/P voltage V<sub>out</sub> in the circuit given below for different values of V<sub>a</sub>, V<sub>b</sub>.

(04 Marks)

## 10EC56

- b. Design Bus Arbitration logic for n line bus. (10 Marks)

- c. Consider  $\lambda$  based design rules and 5 $\mu$ m technology. How many nmos 8:1 inverter  $\left(Z_{pu} = \frac{16\lambda}{2\lambda} \text{ and } Z_{pd} = \frac{2\lambda}{2\lambda}\right) \text{ can be driven by a minimum size conductor which is 3}\lambda \text{ wide and 1}\mu\text{m thick? Assume J}_{th} = 1\text{mA/(}\mu\text{m})^2 \text{ , } R_s = 10\text{K}\Omega \text{ / }\square \text{ , } V_{DD} = 5\text{V}. \tag{06 Marks}$

- 6 a. Discuss the 4 phase clocking scheme to avoid the problem of cascading in dynamic CMOS logic. (06 Marks)

- b. What are the adder enhancement techniques? Briefly explain.

(04 Marks)

c. Write and explain 6 - bit carry select adder.

(10 Marks)

- 7 a. Write and explain 4 Transistor dynamic and 6 Transistor static CMOS memory cell with sense amplifier. (12 Marks)

- b. Explain the one transistor dynamic memory cell emphasizing three plate capacitor.

(08 Marks)

- **8** Write short notes on:

- a. Latch up.

(07 Marks)

b. Nature of failures in CMOS.

(06 Marks)

c. I/O pads.

(07 Marks)